第三世代半導体材料であるシリコンカーバイド(SiC)は、その優れた物理的特性と高出力エレクトロニクスにおける有望な用途により、大きな注目を集めています。従来のシリコン(Si)やゲルマニウム(Ge)半導体とは異なり、SiCは広いバンドギャップ、高い熱伝導率、高い絶縁破壊電界、そして優れた化学的安定性を備えています。これらの特性により、SiCは電気自動車、再生可能エネルギーシステム、5G通信、その他高効率・高信頼性が求められる用途のパワーデバイスに最適な材料となっています。しかし、その高い可能性にもかかわらず、SiC業界は深刻な技術的課題に直面しており、それが普及への大きな障壁となっています。

1. SiC基板: 結晶成長とウエハ製造

SiC基板の製造はSiC産業の基盤であり、最大の技術的障壁となっています。SiCは融点が高く、結晶化学が複雑なため、シリコンのように液相から成長させることができません。その代わりに、主要な方法は物理気相輸送(PVT)法です。これは、高純度のシリコンと炭素粉末を制御された環境下で2000℃を超える温度で昇華させる方法です。この成長プロセスでは、高品質の単結晶を製造するために、温度勾配、ガス圧、流動ダイナミクスを精密に制御する必要があります。

SiCには200種類以上のポリタイプがありますが、半導体用途に適したものはごくわずかです。マイクロパイプや貫通転位といった欠陥はデバイスの信頼性に深刻な影響を与えるため、適切なポリタイプを確保しつつ、これらの欠陥を最小限に抑えることが重要です。成長速度は遅く、多くの場合1時間あたり2mm未満であるため、シリコン結晶の成長時間はわずか数日であるのに対し、1個のブールの成長時間は最大1週間にも及びます。

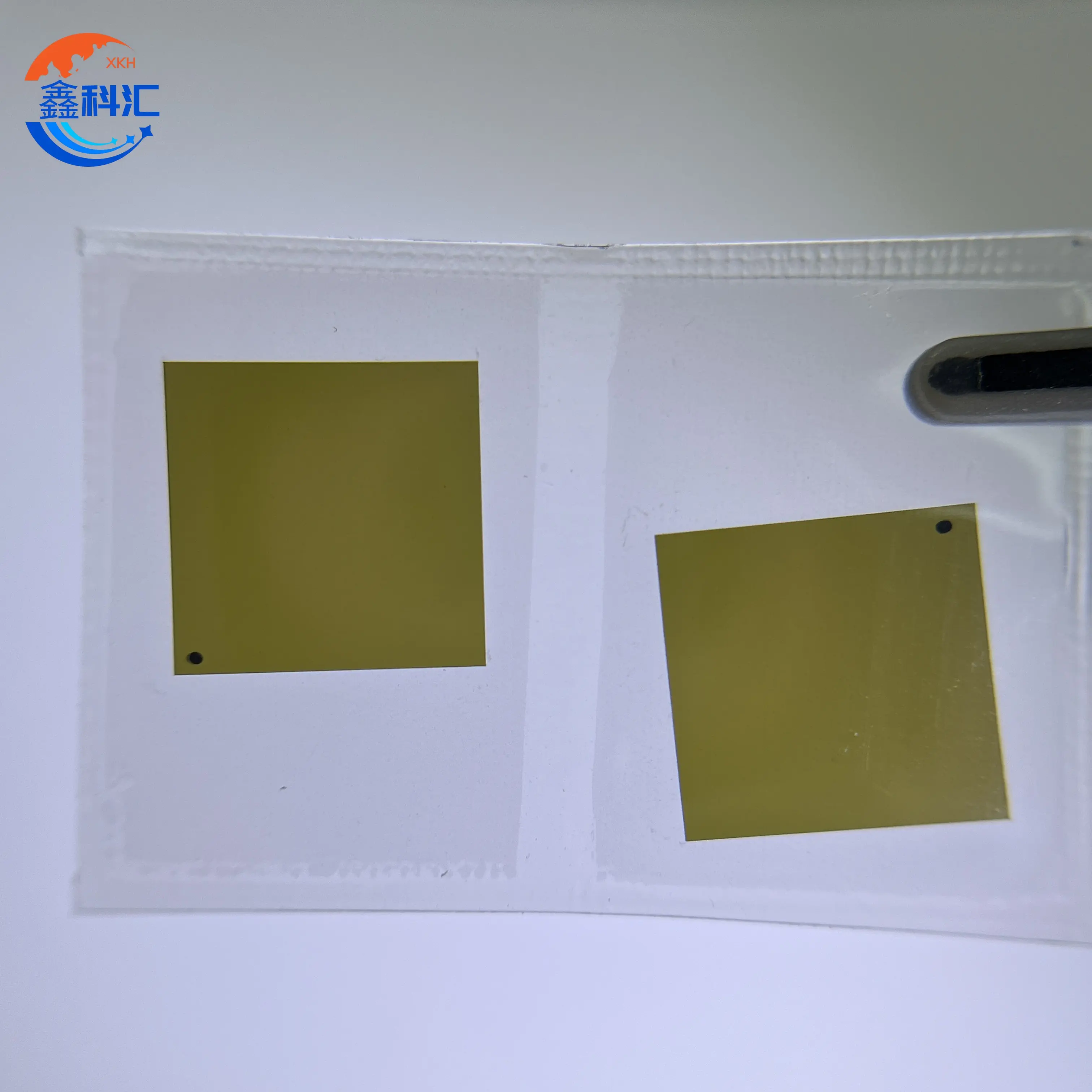

結晶成長後、SiCはダイヤモンドに次ぐ硬度を持つため、スライス、研削、研磨、洗浄といった工程は非常に困難です。これらの工程では、表面の完全性を維持しながら、マイクロクラック、エッジの欠け、表面下の損傷を回避する必要があります。ウェーハの直径が4インチから6インチ、さらには8インチへと拡大するにつれて、熱応力を制御し、欠陥のない膨張を実現することはますます複雑になります。

2. SiCエピタキシー:層の均一性とドーピング制御

基板上へのSiC層のエピタキシャル成長は、デバイスの電気的性能がこれらの層の品質に直接依存するため、極めて重要です。化学気相成長(CVD)は主要な方法であり、ドーピングの種類(n型またはp型)と層の厚さを精密に制御できます。定格電圧が高くなるにつれて、必要なエピタキシャル層の厚さは数マイクロメートルから数十マイクロメートル、さらには数百マイクロメートルにまで増加する可能性があります。厚い層全体にわたって均一な厚さ、一貫した抵抗率、そして低い欠陥密度を維持することは極めて困難です。

エピタキシー装置とプロセスは現在、世界的に数社のサプライヤーによって独占されており、新規メーカーにとって参入障壁が高くなっています。たとえ高品質の基板を使用しても、エピタキシャル制御が不十分だと、歩留まりの低下、信頼性の低下、そしてデバイス性能の最適化が不十分になる可能性があります。

3. デバイス製造:精密プロセスと材料の適合性

SiCデバイスの製造には更なる課題があります。SiCは融点が高いため、従来のシリコン拡散法は効果的ではなく、代わりにイオン注入法が用いられます。ドーパントを活性化するには高温アニールが必要であり、結晶格子の損傷や表面劣化のリスクがあります。

高品質な金属接点の形成もまた、極めて重要な課題です。パワーデバイスの効率向上には、低い接触抵抗(<10⁻⁵ Ω·cm²)が不可欠ですが、NiやAlといった一般的な金属では熱安定性に限界があります。複合メタライゼーション方式は安定性を向上させますが、接触抵抗を増加させるため、最適化が非常に困難になります。

SiC MOSFETはインターフェースの問題にも悩まされています。SiC/SiO₂インターフェースはトラップ密度が高く、チャネル移動度と閾値電圧の安定性が制限されることがよくあります。スイッチング速度が速いと寄生容量とインダクタンスの問題がさらに悪化するため、ゲート駆動回路とパッケージングソリューションの慎重な設計が求められます。

4. パッケージングとシステム統合

SiCパワーデバイスは、シリコンデバイスよりも高い電圧と温度で動作するため、新たなパッケージング戦略が必要となります。従来のワイヤボンディングモジュールでは、熱性能と電気性能の限界により不十分です。SiCの能力を最大限に引き出すには、ワイヤレスインターコネクト、両面冷却、デカップリングコンデンサ、センサー、駆動回路の統合といった高度なパッケージング手法が不可欠です。導通抵抗、寄生容量の低減、スイッチング効率の向上により、ユニット密度の高いトレンチ型SiCデバイスが主流になりつつあります。

5. コスト構造と業界への影響

SiCデバイスの高コストは、主に基板とエピタキシャル材料の製造コストに起因しており、これらを合わせると製造コスト全体の約70%を占めます。高コストにもかかわらず、SiCデバイスはシリコンに対して優れた性能を備えており、特に高効率システムにおいては顕著です。基板とデバイスの生産規模と歩留まりが向上するにつれて、コストは低下すると予想され、自動車、再生可能エネルギー、産業用途におけるSiCデバイスの競争力は向上するでしょう。

結論

SiC産業は半導体材料における大きな技術的飛躍を象徴していますが、複雑な結晶成長、エピタキシャル層制御、デバイス製造、そしてパッケージングといった課題によって、その導入は制約を受けています。これらの障壁を克服するには、精密な温度制御、高度な材料処理、革新的なデバイス構造、そして新たなパッケージングソリューションが必要です。これらの分野における継続的なブレークスルーは、コスト削減と歩留まり向上を実現するだけでなく、次世代パワーエレクトロニクス、電気自動車、再生可能エネルギーシステム、そして高周波通信アプリケーションにおけるSiCの潜在能力を最大限に引き出すことにつながります。

SiC 業界の将来は、材料の革新、精密製造、デバイス設計の統合にあり、シリコンベースのソリューションから高効率、高信頼性のワイドバンドギャップ半導体への移行を推進します。

投稿日時: 2025年12月10日