シリコン ウェーハ基板上にシリコン原子の追加層を成長させることには、いくつかの利点があります。

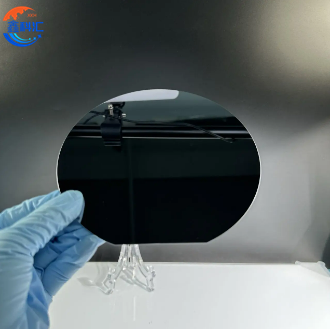

CMOS シリコン プロセスでは、ウェーハ基板上のエピタキシャル成長 (EPI) が重要なプロセス ステップです。

1、結晶品質の向上

初期の基板欠陥および不純物:製造プロセスにおいて、ウェーハ基板には特定の欠陥や不純物が含まれる場合があります。エピタキシャル層の成長により、基板上の欠陥や不純物濃度が低い高品質の単結晶シリコン層が生成され、これは後続のデバイス製造にとって非常に重要です。

均一な結晶構造: エピタキシャル成長により、より均一な結晶構造が確保され、基板材料の粒界や欠陥の影響が軽減され、ウェーハ全体の結晶品質が向上します。

2、電気性能を向上させる。

デバイス特性の最適化:基板上にエピタキシャル層を成長させることで、シリコンのドーピング濃度と種類を正確に制御し、デバイスの電気的性能を最適化できます。例えば、エピタキシャル層のドーピングを微調整することで、MOSFETの閾値電圧やその他の電気的パラメータを制御することができます。

リーク電流の削減: 高品質のエピタキシャル層は欠陥密度が低いため、デバイスのリーク電流が削減され、デバイスのパフォーマンスと信頼性が向上します。

3、電気性能を向上させる。

微細化:プロセスノード(7nm、5nmなど)が微細化するにつれ、デバイスの微細化は進み、より洗練された高品質の材料が求められます。エピタキシャル成長技術はこうした要求に応え、高性能・高密度の集積回路の製造を支えています。

耐圧の向上:エピタキシャル層はより高い耐圧で設計することができ、これは高出力・高電圧デバイスの製造に不可欠です。例えば、パワーデバイスでは、エピタキシャル層によってデバイスの耐圧が向上し、安全な動作範囲が広がります。

4、プロセス互換性と多層構造

多層構造:エピタキシャル成長技術は、基板上に層ごとに異なるドーピング濃度とドーピングタイプを持つ多層構造を成長させることを可能にします。これは、複雑なCMOSデバイスの製造や3次元集積化に非常に有益です。

互換性: エピタキシャル成長プロセスは既存の CMOS 製造プロセスと高い互換性があり、プロセス ラインに大きな変更を加えることなく、現在の製造ワークフローに簡単に統合できます。

概要:CMOSシリコンプロセスにおけるエピタキシャル成長の応用は、主にウェーハ結晶品質の向上、デバイスの電気的性能の最適化、先進プロセスノードのサポート、そして高性能・高密度集積回路製造の要求への対応を目的としています。エピタキシャル成長技術は、材料のドーピングと構造の精密な制御を可能にし、デバイスの全体的な性能と信頼性を向上させます。

投稿日時: 2024年10月16日