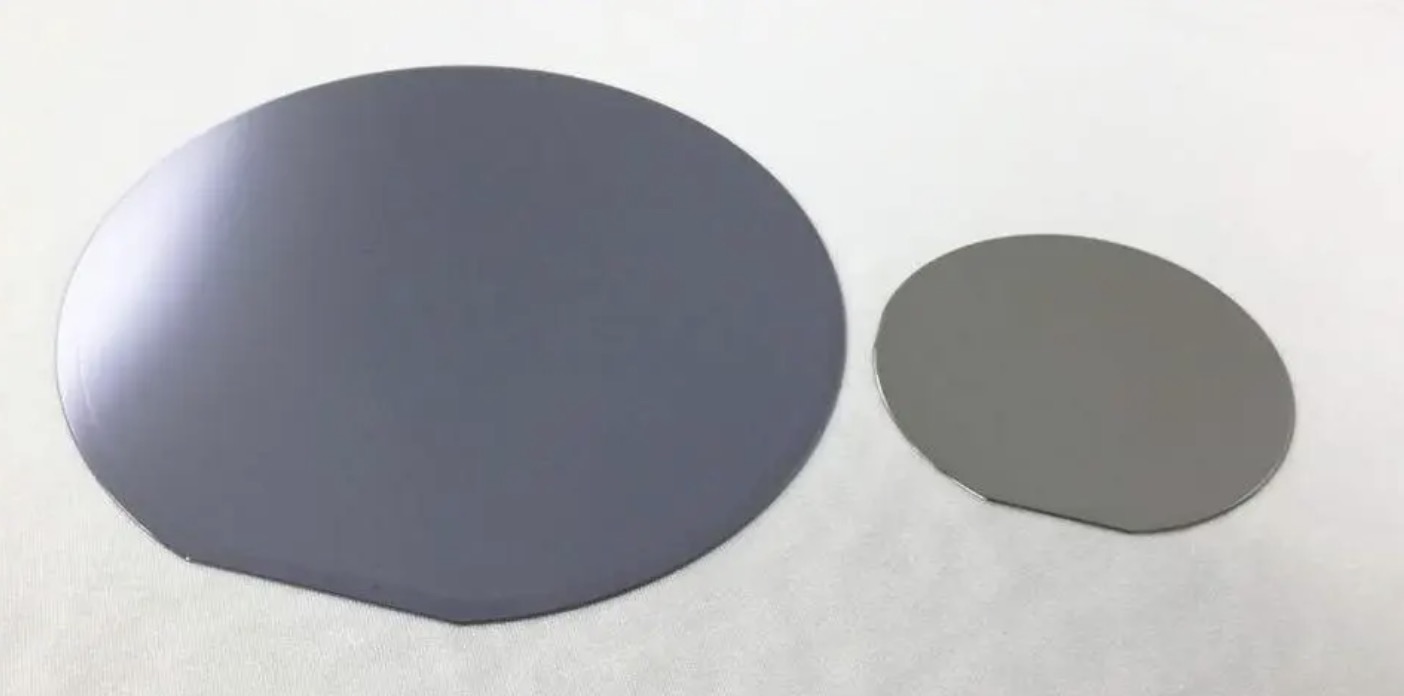

6インチSiCエピタキシャルウェーハN/Pタイプはカスタマイズ可能

シリコンカーバイドエピタキシャルウェーハの製造プロセスは、化学気相成長(CVD)技術を用いた方法です。関連する技術原理と製造プロセスの手順は次のとおりです。

技術原理:

化学蒸着法:気相中の原料ガスを利用し、特定の反応条件下で分解して基板上に堆積させ、目的の薄膜を形成します。

気相反応:熱分解または分解反応により、気相中の各種原料ガスが反応室内で化学的に変化します。

準備プロセスの手順:

基板処理:基板は表面洗浄と前処理が施され、エピタキシャル ウェーハの品質と結晶性が確保されます。

反応室のデバッグ: 反応室の温度、圧力、流量などのパラメータを調整して、反応条件の安定性と制御を確保します。

原料供給:必要なガス原料を反応室に供給し、必要に応じて混合し、流量を制御します。

反応プロセス: 反応室を加熱することにより、ガス状の原料が反応室内で化学反応を起こし、目的の堆積物、つまりシリコンカーバイド膜を生成します。

冷却と除荷:反応の最後に、温度を徐々に下げて反応室内の堆積物を冷却し固化させます。

エピタキシャル ウェーハのアニールおよび後処理: 堆積されたエピタキシャル ウェーハは、電気的特性と光学的特性を改善するためにアニールおよび後処理されます。

シリコンカーバイドエピタキシャルウェーハ製造プロセスの具体的な手順と条件は、具体的な設備や要件によって異なる場合があります。上記は一般的なプロセスフローと原理を示したものであり、具体的な操作は実際の状況に応じて調整・最適化する必要があります。

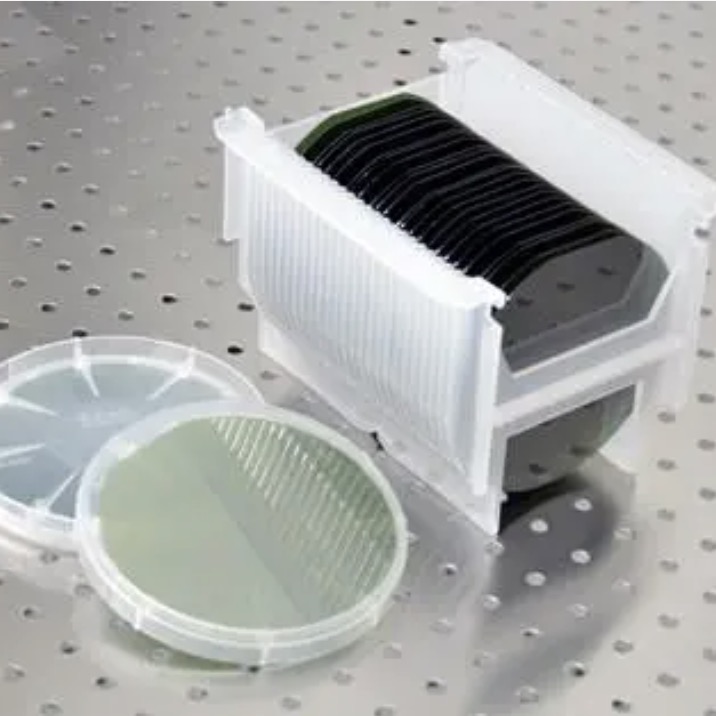

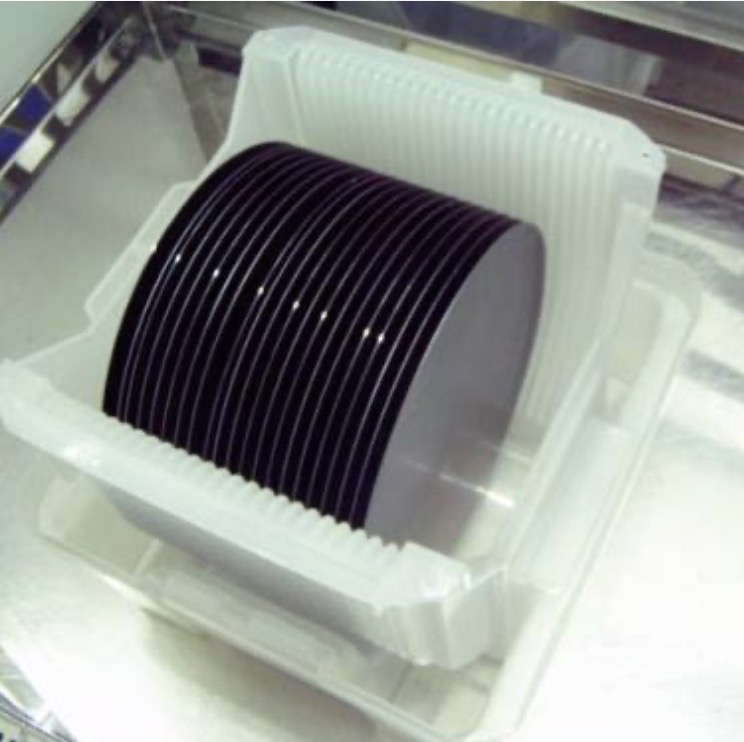

詳細図

関連製品

ここにメッセージを書いて送信してください